# 5 Zusammengesetzte und reguläre Schaltungsstrukturen

- regelmäßig aufgebaute (reguläre) Schaltungsstrukturen implementieren jeweils eine größere Zahl an Gatterfunktionen

- wichtigste Vertreter: Speicher, programmierbare Logikbausteine, Gate Arrays

- Vorteile

- oftmals bessere Flächeneffizienz

- Vereinfachung und Beschleunigung des Entwurfs

- Probleme

- Zeitverhalten, Störungen, Flächeneffizienz bei weniger "regelmäßigen" Funktionen

240

# **Speicher**

- wichtigste Gruppe der regulären Schaltungsstrukturen

- wesentliche Kenndaten

- Speicherkapazität

- maximale Zugriffszeit t<sub>AC</sub>

- minimale Zykluszeit t<sub>CYC</sub>

### Probleme des Speicherentwurfs

- hohe Flächeneffizienz erfordert

- große Speichermatrizen ⇒ lange Leitungen mit hohen Kapazitäten (RC-Leitung)

- kleine Speicherzellen ⇒ geringe Treiberfähigkeit

- ⇒ hohe Zugriffszeiten

- heute ≥ 512 Zeilen und Spalten pro Speicherblock

- Ansatz:

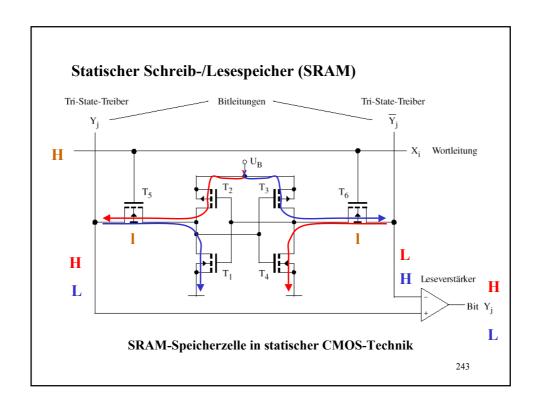

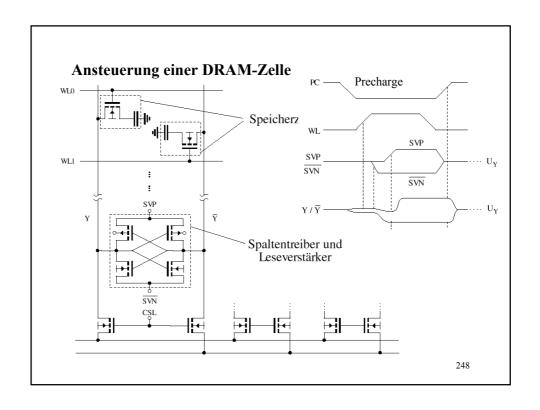

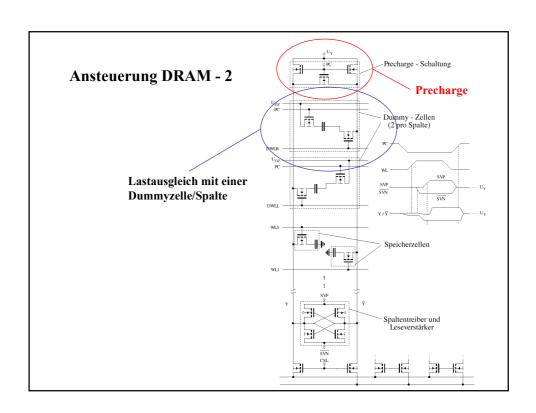

- verringerte Störabstände und symmetrische Signalübertragung mit Precharge auf den Bitleitungen

- empfindliche Leseverstärker (mit  $\Delta U < 1 \text{mV}$ )

- $\bullet \quad \mathbf{t}_{\mathrm{AC}} = \mathbf{t}_{\mathrm{CYC}}$

- Beispieldaten: Kapazität = 1MByte, t<sub>AC</sub> < 5ns (Motorola: http://www.mot.com/SPS/FastSRAM/productupdate/ddr.html)

# **Dynamische Schreib-/Lesespeicher (DRAM)**

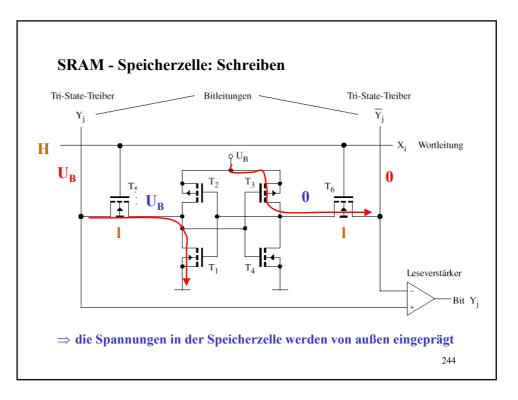

- Schreiben wie statischer Speicher

- Lesen mit Ladungsumverteilung von C auf  $C_L$   $C << C_L \qquad U_{Yj} = U_C \cdot \frac{C}{C + C_L}$   $\Rightarrow \text{,,zerstörendes" Lesen, sehr kleines Lesesignal}$

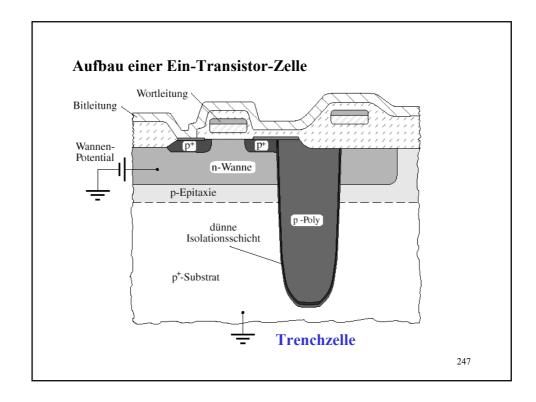

- ⇒ Maximierung der Kapazitäten C erforderlich

### Ansteuerung des DRAM - 3

• Rückschreiben nach jedem Lesevorgang

```

\Rightarrow t<sub>CYC</sub> > t<sub>AC</sub>

Beispiel: t<sub>AC</sub> = 20ns, t<sub>CYC</sub> = 70ns (Samsung KM416S4030C)

```

- Auffrischen der Speicherzellen (Refresh) durch rechtzeitiges Lesen jeder Speicherzeile

- Beispiel: 1024 Zeilen, Refresh alle 16ms → 1 Refreshvorgang/16 $\mu$ s d.h. bei  $t_{CYC}$  = 70 ns tritt in weniger als 1% der Fälle ein Zugriffskonflikt auf ⇒ meist vernachlässigbar

- insgesamt komplexe Steuerung

250

#### **SRAM und DRAM**

- der dynamische Speicher hat eine größere Packungsdichte als der statische (>Faktor 4)

- der dynamische Speicher ist langsamer

- ⇒ Speicherhierarchie mit statischem Cache

- $\Rightarrow$  blockweise Zugriffe auf lange Speicherzeilen: SDRAM, SLDRAM , RAMBUS

- aufgrund der einfacheren Ansteuerung werden statische Speicher für Aufgaben mit geringen Anforderungen an die Speicherkapazität eingesetzt (Puffer, Registerfiles, ...)

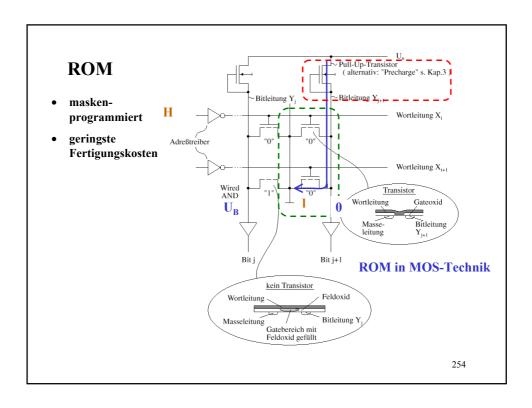

### Festwertspeicher

- Wert kann nur gelesen werden

- ROM (Read Only Memory):

Der Speicherinhalt wird bereits bei der Fertigung festgelegt und ist daher nicht änderbar.

#### • PROM (Programmable ROM)

Der Speicherinhalt kann einmalig vom Anwender einprogrammiert werden, ist jedoch danach nicht mehr änderbar.

#### • EPROM (Erasable PROM)

Der Speicherinhalt wird vom Anwender einprogrammiert und kann durch UV-Strahlung wieder gelöscht werden.

#### • EEPROM (Electrically Erasable PROM)

Der Speicherinhalt ist wie beim EPROM löschbar, allerdings elektrisch.

#### • Flash EPROM

Der Löschvorgang wird wie beim EEPROM elektrisch aktiviert. Die Löschung erfolgt jedoch sektorenweise.

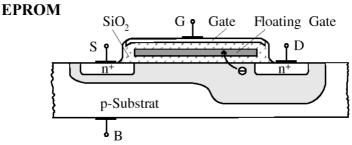

### FAMOS-Transistor zur Realisierung einer EPROM-Speicherzelle

- Unterschied zu ROM: Speicherzelle

- durch Anlegen einer hohen Spannung  $U_{DS}$  (z.B.  $U_{DS}$  = 17V) entsteht bei  $U_{SB}$  = 0 eine hohe Feldstärke nahe dem Drain-Bereich, die zur Generierung "heißer" Elektronen führt

- durch Anlegen einer hohen Spannung U<sub>GS</sub> (z.B. U<sub>GS</sub> = 24V) werden diese Elektronen teilweise durch das Gateoxid auf das isolierte Floating Gate gezogen ⇒ Schwellspannung steigt

- Entfernen der Elektronen durch UV-Strahlung

256

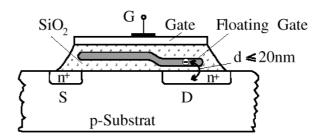

#### **EEPROM**

Transistor einer EEPROM-Speicherzelle

- Floating Gate wie EPROM, aber dünneres Oxid über Drain oder Kanal erlaubt Tunneln von Ladungsträgern (statt Avalanche-Durchbruch wie beim FAMOS)

- $\begin{array}{l} \bullet \quad \quad & Effekt \ umkehrbar \ zur \ elektrischen \ Löschung \\ Problem: \ negative \ Schwellspannung \ U_{th} \ m\"{o}glich, \ daher \ zweiter \\ Transistor \ erforderlich \\ \end{array}$

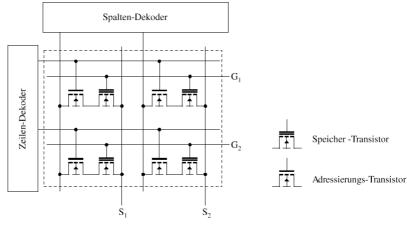

# **EEPROM Speichermatrix**

Adressierungs-Transistor trennt nicht adressierte EEPROM-Zellen von den Bitleitungen

258

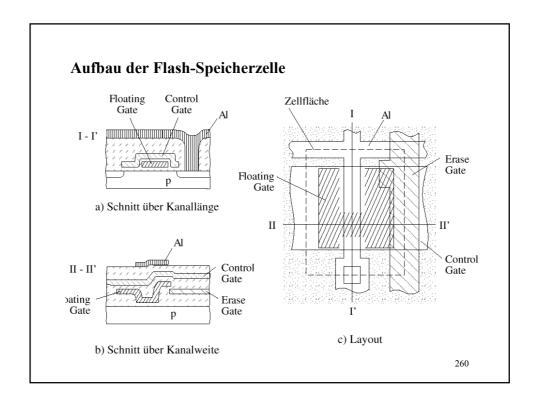

# Flash-Speicher

- Kombination von Adressierungs-Transistor und Speichertransistor in einem komplexen Element

- gemeinsames Löschen von Blöcken über zusätzliches Erase-Gate (Flash)

⇒ schneller, einfacher Löschvorgang

# Einsatzbereiche der Speicher

- Verwendung als Programm-, Daten- oder Pufferspeicher

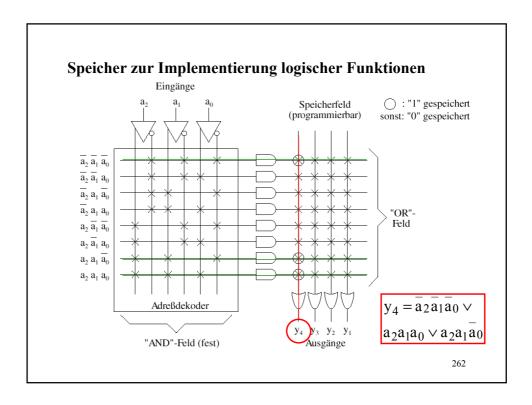

- Implementierung logischer Funktionen in zweistufiger Logik in disjunktiver kanonischer Form (disjunktive kanonische Form: Aufzählung der Minterme)

# Speicher zur Implementierung logischer Funktionen - 2

- Vorteile: hohe Packungsdichte der Minterme, garantiertes Zeitverhalten

- Nachteile: 2<sup>n</sup> Wortleitungen für n Eingangsvariablen

Beispiel: 8 Ausgangsvariablen, 20 Eingangsvariablen: 1 MByte

Speicherkapazität

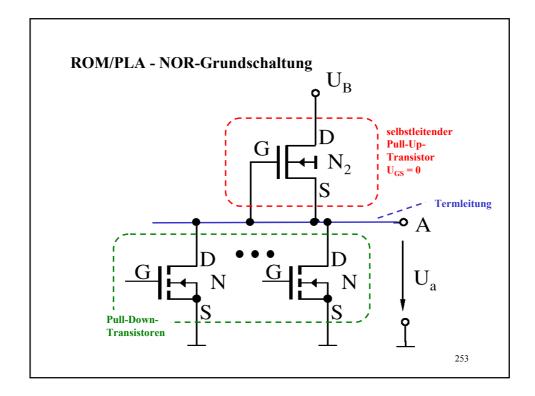

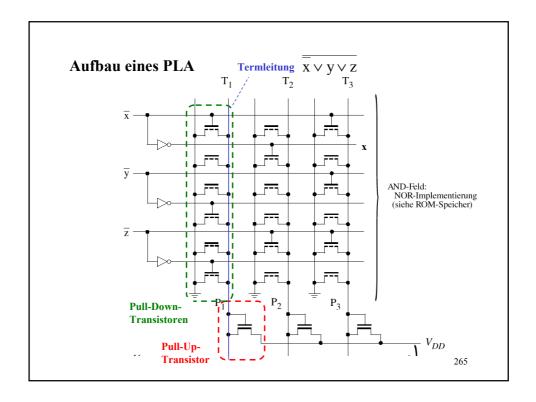

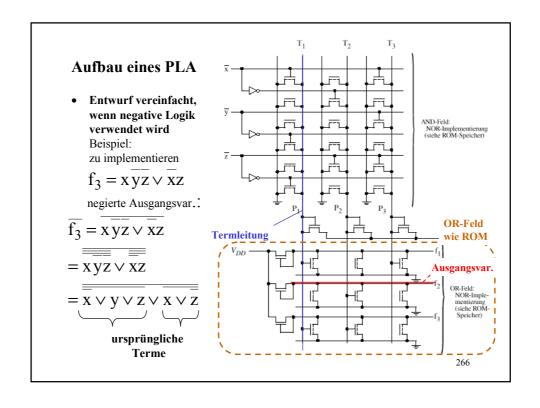

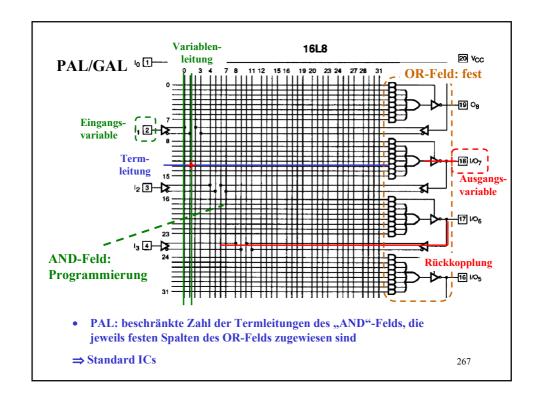

# Programmierbare Logik PLA und PAL

- Problem des Speichers: stets Implementierung jedes Minterms

- PLA: Ersatz des Adreßdecoders durch ein programmierbares "AND"-Feld ⇒ Implementierung der optimierten DNF statt der DKF

Im Beispiel:

$$y_4 = \underbrace{a_2 a_1 a_0 \lor a_2 a_1 a_0}_{\text{DKF}} = \underbrace{a_2 a_1 a_0 \lor a_2 a_1}_{\text{DNF}}$$

• Übliche Implementierung als NOR-NOR Funktion

### PLA/PAL - Bewertung

- einfache Implementierung von logischen Funktionen

- Standard-ICs für Produktion und Labor verfügbar sehr schnell (t<sub>pd</sub> ≤ 5ns)

Anwendungen: Adreßdekodierung, Speichersteuerung, Reset-Logik, ...

- PALs mit Flip-Flops zu Implementierung von Automaten

- hochdichte Implementierung auf der integrierten Schaltung (Anwendung z.B. Befehlsdekodierung)

- nur zweistufige DNF implementierbar,

- ⇒ weniger effizient bei komplexen Funktionen mit vielen Eingängen, langsam bei Verwendung der Rückkopplung

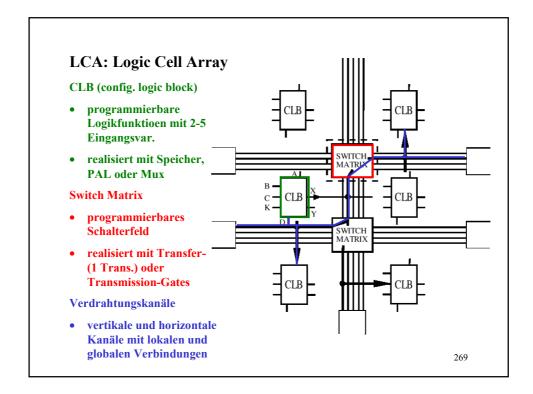

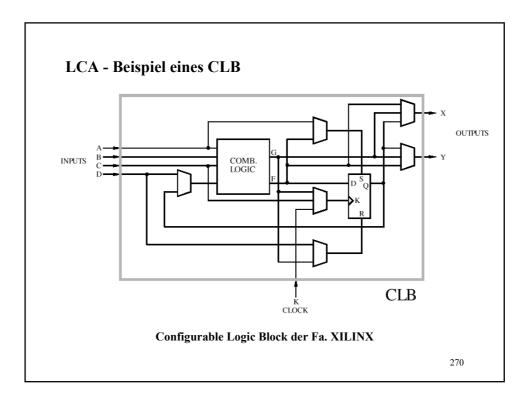

### **LCA - 2**

- andere Bezeichnung: FPGA (field programmable gate array)

- Programmierung als RAM, PROM, EPROM, EEPROM, Flash EPROM

- aufwendige, aber sehr flexible Schaltungsstruktur

- verfügbar bis über 10 Mio Gatteräquivalente + Speicher ⇒ ganze Schaltungssysteme implementierbar

- rekonfigurierbare Systeme mit programmierbarer Funktion als Ersatz für programmierbare Prozessoren oder späte Änderung der Schaltungsfunktion möglich

- programmiert durch Synthesewerkzeuge

- Probleme:

- hoher Preis bzw. Fläche bei größeren LCAs

- Verlustleistung

- begrenzte Schaltgeschwindigkeit (spezifiziert: max. ca. 400MHz Taktfrequenz)