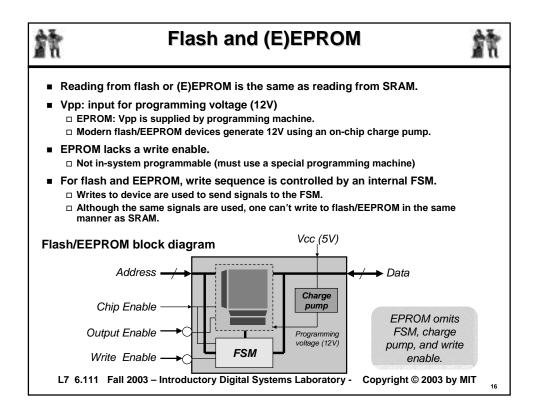

| Read-Write Memory |                      | Non-Volatile<br>Read-Write<br>Memory | Read-Only<br>Memory |

|-------------------|----------------------|--------------------------------------|---------------------|

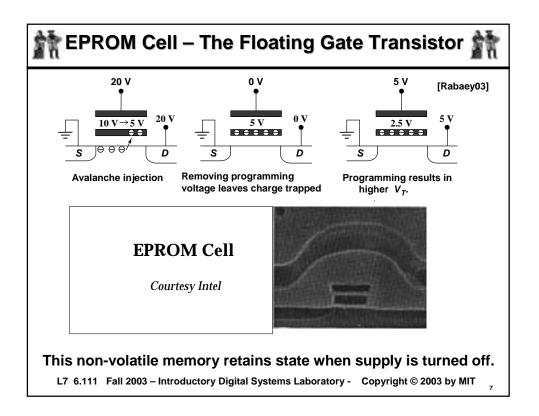

| Random<br>Access  | Non-Random<br>Access | EPROM<br>E <sup>2</sup> PROM         | Mask-Programmed     |

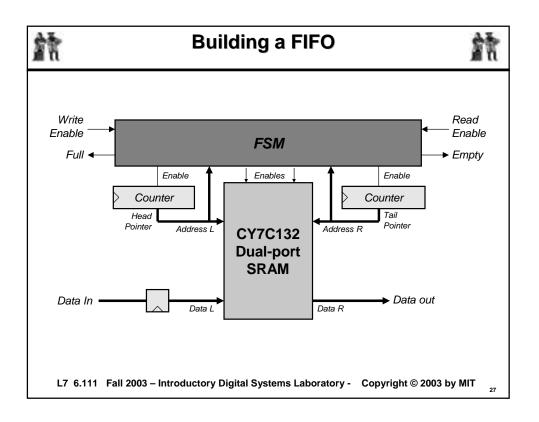

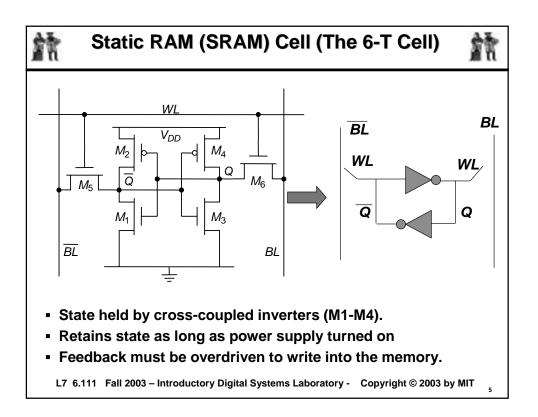

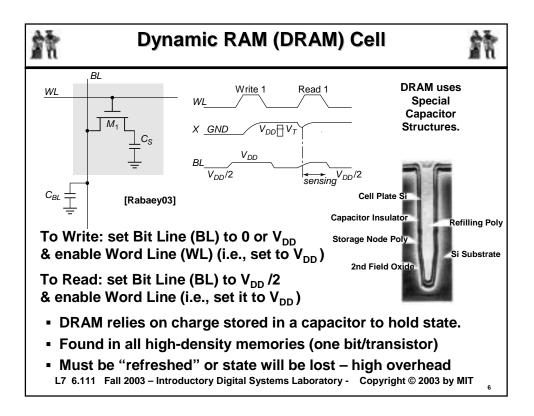

| SRAM<br>DRAM      | FIFO<br>LIFO         | FLASH                                |                     |

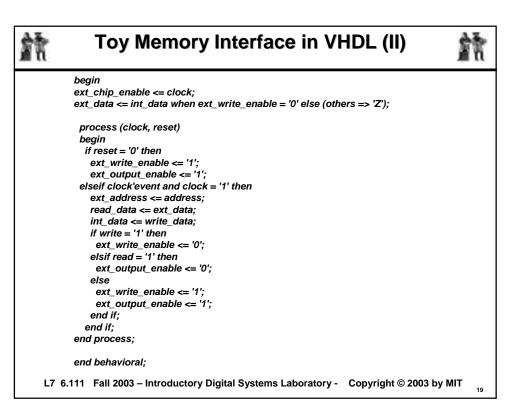

| ñ  | Toy Memory Interface in VHDL (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | n      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|    | library ieee;<br>use ieee.std_logic_1164.all;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

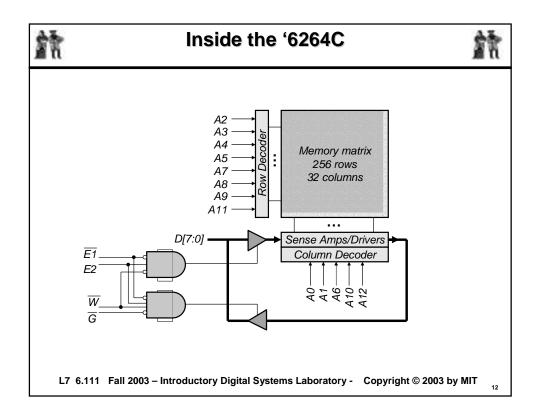

|    | <pre>entity mem_int is port (clock : in std_logic;     reset : in std_logic;     write : in std_logic;     read : in std_logic;     address : in std_logic_vector(12 downto 0);     write_data : in std_logic_vector(7 downto 0);     read_data : out std_logic_vector(7 downto 0);     ext_chip_enable : out std_logic;     ext_write_enable : out std_logic;     ext_output_enable : out std_logic;     ext_address : out std_logic_vector(12 downto 0);     ext_data : inout std_logic_vector(7 downto 0);     ext_data : inout std_logic_vector(7 downto 0);     ext_data : inout std_logic_vector(12 downto 0); ext_data : inout std_logic_vector(7 downto 0)); end mem_int;</pre> |        |

|    | architecture behavioral of mem_int is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| L7 | signal int_data : std_logic_vector(7 downto 0);<br>(cont. on next viewgraph)<br>6.111 Fall 2003 – Introductory Digital Systems Laboratory - Copyright © 2003 k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ov MIT |